3. Design Full Adder

전 포스팅에서 gate하나를 vivado를 통해 simulation까지 해보았다.

이번 포스팅에서는 논리회로 시간에 combination logic부분을 다뤘었는데 해당 내용을 실제로 설계해보고 시뮬레이션까지 돌려보는것을 해보도록 하겠다.

전 포스팅에서 어떻게 만드는지를 설명안한것같아 step by step으로 한번 설명해보면,

1. Create Project -> 위치 설정후 생성

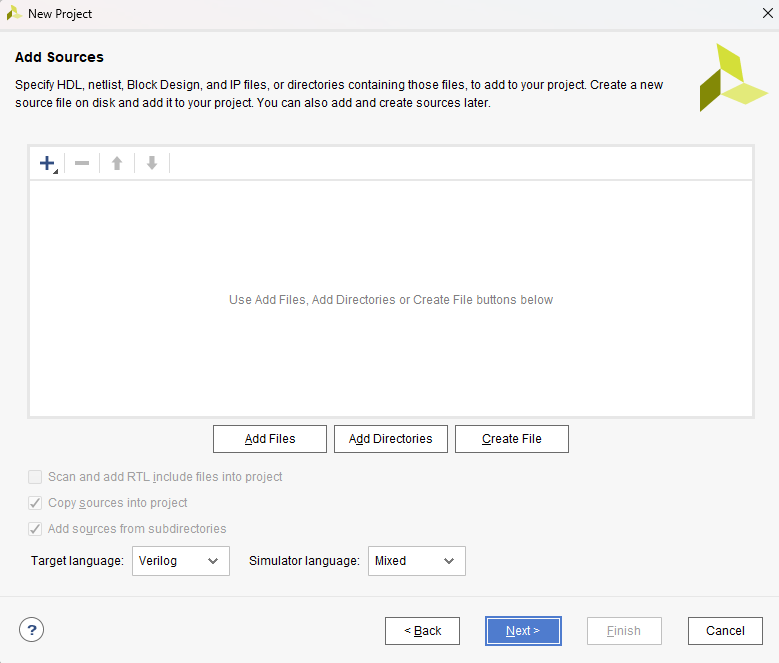

순서대로 따라가면

이런 화면이 나온다.

여기서 Create File을 눌러준 후

설계할 이름을 적어준 뒤 ok 누르기

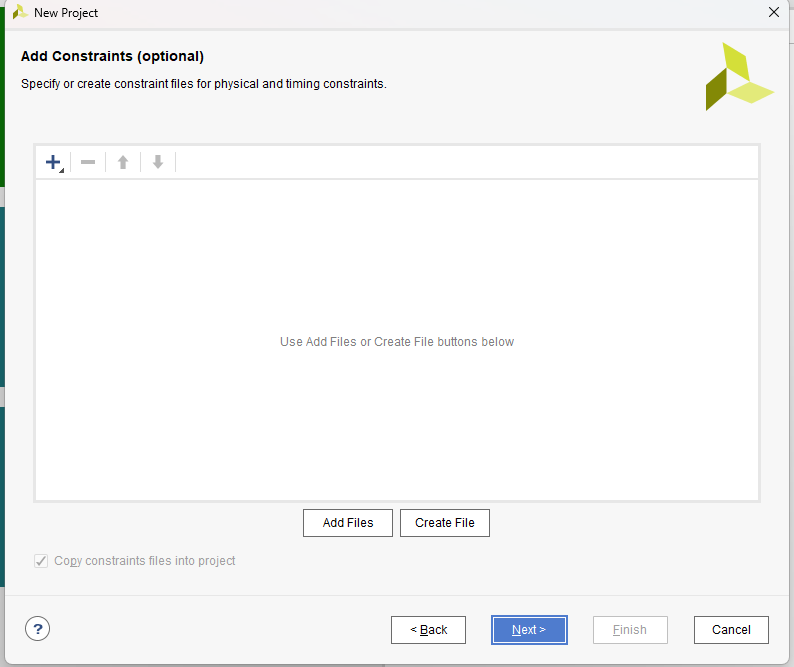

다 만들고나서 다시 Add source를 눌러 3번째꺼를 눌러준다. (test bench용도)

이렇게 만들어주고,

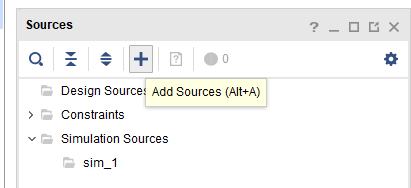

source칸에 이렇게 보이면 성공이다.

이제 해당 부분 더블 클릭해서 Verilog coding을 해주면 된다.

이제 Full Adder 설계를 진행해보자.

Logic circuit_4: Combination Logic(1)

논리회로는 combination logic과 sequential logic 2개로 분류할 수 있다.input이 들어가면 바로 output이 나오는 combination logic에 대해 며칠에 거쳐 포스팅할 예정이다.또한, 해당 내용 포스팅이 끝나면 관련

ksh9-9.tistory.com

해당 포스팅에서 가져온 그림이다.

이를 토대로 Verilog coding을 진행하면,

위와같이 설계한것을 그대로 코딩을 해준 뒤에 simulation을 돌려보면,

위와같은 결과가 나오게 되는데 무언가 이상하지 않은가?

10ns에서 sum이 1이 나와야하는데 0이 나오고있는것을 볼 수 있다.

코딩한것은 이론적으로 도출된값을 그대로 사용하는 것이기 때문에 이러면 이렇게 코딩한 이유의 부분을 찾아 돌아가야한다.

Sum부분에서 X'YC_in'으로해야하는데 X'이 아닌 X를 사용한 것을 볼 수 있다. 해당 부분을 수정하여 다시 코딩후 시뮬레이션을 돌리게 되면

원하는값이 출력되는것을 볼 수 있다.

여기서 틀린부분을 발견하고 디버깅하는과정자체를 보여준 이유가 있다.

앞으로 어떤 작업을 하던간에 사람이 작업을 하는 것이기 때문에 크건 작건 한번에 원하는 결과를 못 얻을 가능성이 훨씬 높다. 일단 작업을 시작한뒤에 확인해보면서 내가 원하는 값과 다른 부분이 있다면 해당 부분을 짠 부분부터 찾아가서 오류를 수정하는 과정이 매우 중요하다고 생각한다.

지난학기 가속기 시스템 설계 프로젝트를 하면서 느낀건데 원하는 결과가 나오지 않을때 코드만 뚫어져라 쳐다보고 다시 검토하면 99%는 발견하지 못한다. 위처럼 결과를 보고 오류가 발생한 부분부터 찾아서 돌아가야 해결이 가능하다라는것을 말해주고 싶다.

main code로 돌아와 몇가지 수정하고 싶은곳이 있다. 위에서는 C_in과 Sum을 사용하였지만 우리에게 익숙한대로 원큐에 결과를 보는게 훨씬 보기 편하다.

설계한 module과 testbench를 위와같이 수정하게 되면 똑같이 작동하게 된다.

혹은,

이렇게 코딩을 해도된다.

마지막부분에 사용한 것은 concatenation이라는 건데, 여러개의 bit를 연결시켜주는 방식이다.

여기까지가 논리회로 포스팅에서 정리한 Full Adder를 Verilog 코딩을 한 과정이다.

다음 포스팅에서는 4bit Full Adder 설계를 해 볼 예정이다.