4. Interconnect_2

오늘 포스팅은 Bus로 시작을 하려고한다.

이전 포스팅에서 Data transfer에 관여하는 component들이 interconnect고 그 중 대표적인 예시가 AMBA라는 ARM사에서 만든 standard Protocol이라고 했다. 그렇다면 Bus의 성능 결정 요소는 무엇일까?

정답은 동시에 진행할 수 있는 Data transfer의 개수이다. (얼마나 빠르게 Data를 transfer하는지)

Topology가 정해졌을때 component들이 data를 어떻게 주고받을지 (=Protocol)를 잘 짜줘야하는데

soc의 한 component를 IP로 개발했을때 다른 회사에서 사용할 수 있게 하기 위해서 가장 중요한것은 Logic Wrapper처리이다. Bus를 붙이기위해 어떤 interface를 설계해야하며 (개발한 ip가 어떤 bus에 붙는지에 따라 wrapper의 종류가 달라진다.) IP를 설계하는만큼 집적될 bus interface를 고려하는것도 중요하다.

핵심은

1. IP자체의 동작

2. 연결시 원활한 동작이 일어나는지 (Data transfer시 많은 희생이 있다면 원래의 기대한 성능보다 낮은 성능이 나오기 때문) --> IP와 Bus의 연결

이다.

Vivado에서 synthesis를 할 때 이 합성이라는 행위는 Verilog 코딩한것을 게이트로 변환하는 과정이라는걸 명심하자.

이제 AMBA protocol에 대해 알아보자.

내가 주로 다룬 것은 AXI4지만 그전에 AHB를 정리하고 넘어가려고한다. (생각보다 설명할게 많을거같아서 AHB도 따로 날잡고 포스팅을 추후에 하겠다.)

AHB와 AXI의 차이점은 single share bus VS Crossbar bus인 점이다.

slave0가 master0에 data transfer시 AHB는 slave1이 master1에 전달할 수 없는 반면에, (RDATA Mux출력이 master0로 가는 data를 싣고있기 때문)

AXI의 경우 Mux가 slave, master마다 따로 있기 때문에 salve1이 master1에 전달을 할 수 있다. + read/ write channel이 따로 있기 때문에 동시에 master에서 slave로 data를 옮길 수 있다.

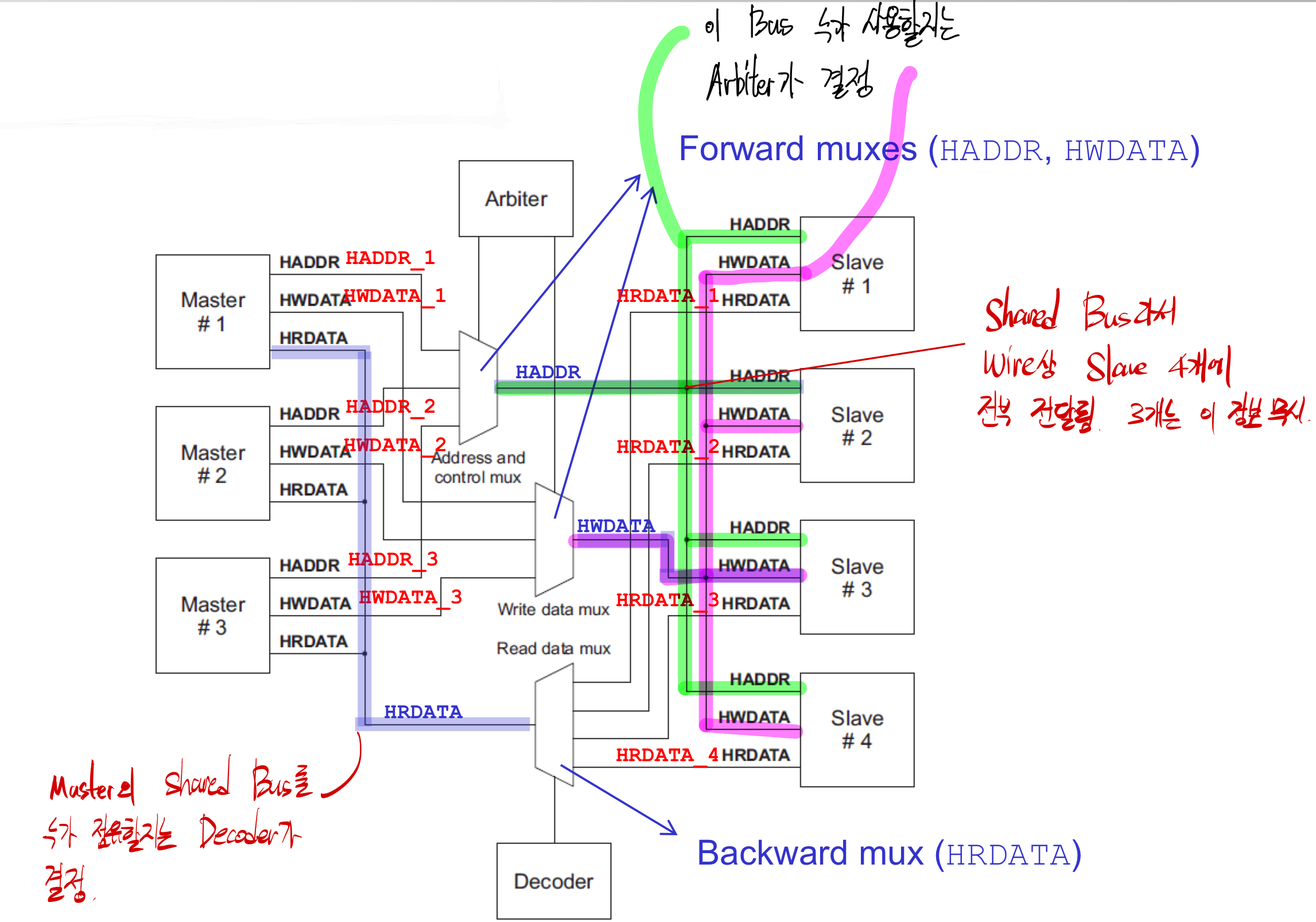

AHB는 single shared bus로 ADDR, WDATA가 각자 4개의 slave에 bus가 연결되고 이 4개의 bus를 어느 master가 점유하는지 arbiter가 결정한다는것을 명심한채로 다음을 보자.

우선 AMBA AHB의 전체 transfer과정은 다음과 같다.

AXI가 메인이니까 AXI를 자세하게 설명해보자면,

1. single cycle edge operation

:clk edge에서 모든 동작이 일어나는것

2. multiple bus masters

: 말그대로 bus master가 여러개

3. seperate address/control and data phases

: address/control 신호와 data 신호가 별도로 전송된다. -> 병렬 작업이 가능하다.

4. unaligned data transfers

5. burst with only the start address

: AHB와 달리 start주소만 전달하면 연속적인 주소의 data들이 burst 형태로 한번에 전달되는 burst mode 지원

6. seperate read and write data channels

: load/store 동시 수행

7. multiple outstanding addresses

:여러개의 주소 요청을 동시에 처리할 수 있음을 의미한다.

8. out of order transaction completion

: transaction이 발생한 순서와는 상관없이 완료 순서가 다를 수 있다.

이렇게 8가지 특징이 있다.

AXI는 ARM사에서 개발한 standard interface protocol이다. interface는 여러 module에서 사용하는 신호들의 집합이라고 전에 이야기한적이 있다. interface를 구현하려면 하드웨어 모듈로 구성해야하며 port가 필연적으로 따라오게된다.

1개의 AXI port = 5개의 Channel로 구성되며,

각 Channel은 여러개의 signal로 나뉘게된다

5개의 channel은 위에 보는 그림과 같다.

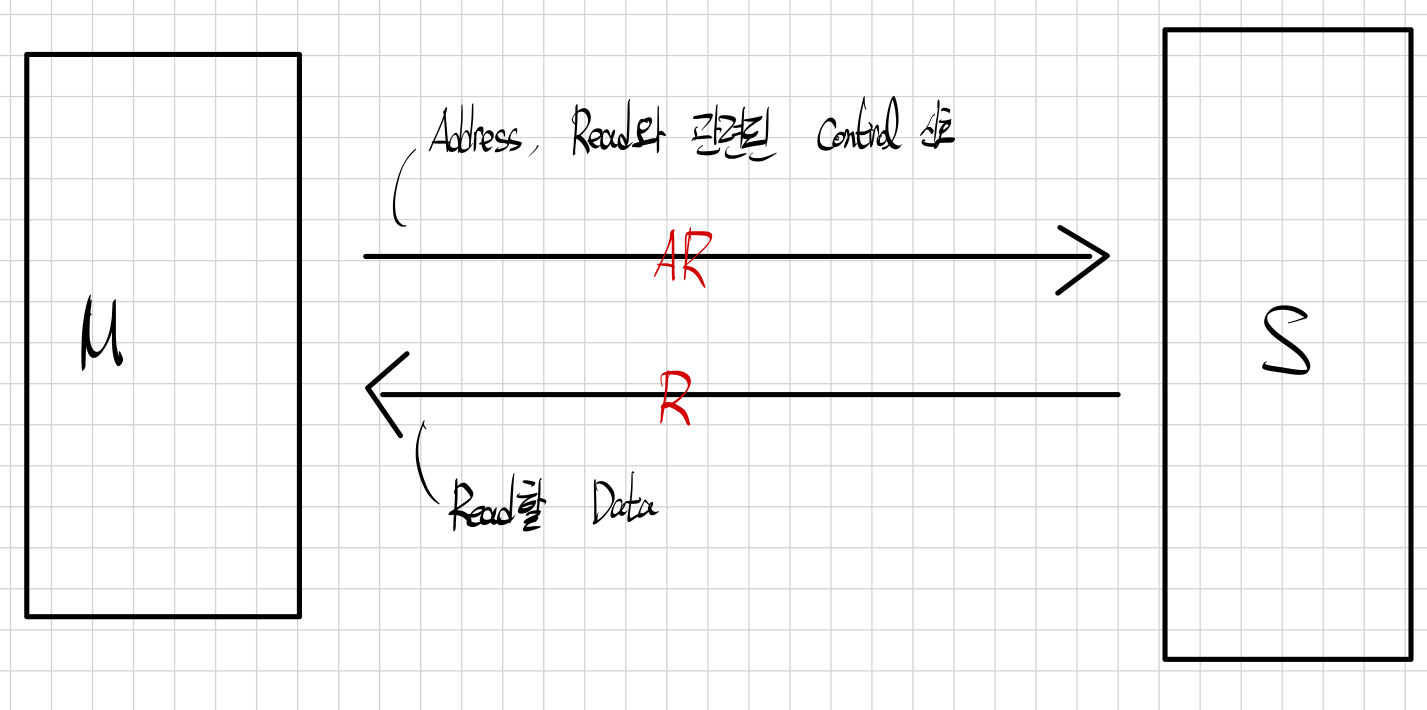

먼저 Read와 Write 과정에 대해 알아보자.

Channel마다 여러 signal이 있다고 했는데, Handshake 개념에 대해 알아야한다.

information을 보낼 준비가 된다면 VALID == 1,

받을준비가 되었다면 READY ==1 이된다.

VALID신호와 READY가 둘 다 1일때 information이 transfer된다.

각 channel마다 READY, VALID신호가 있으며,

ARVALID, ARREADY

RVALID, RREADY

AWVALID, AWREADY

WVALID, WREADY

BVALID, BREADY

이렇게 사용한다.

그 외에도 LEN, SIZE, BURST, LAST, 등등.... 매우 많은 신호가 있는데 관련된것들은 필요할때마다 추가로 설명하도록 하겠다. (control signal들이다.)

예시를 통해 알아보면,

위 예제에서 clk edge에서 VALID == READY == 1 일때 Handshake가 발생하고 이때 해당 채널에 해당하는 information이 transfer된다.

AR channel을 통해 read할 주소를 주고 R channel을 통해 burst mode를 이용해서 data를 read하는것을 볼 수 있다.