이전에 combination logic을 배웠다. input에 의해 output이 바로 결정되는 회로였는데,

오늘 정리할 Sequential Logic은 input과 이전 state에 의해 output이 결정되는 논리 회로이다. 여기서 추가된 것은 "state"라는 개념인데, 이게 왜 필요한걸까?

예시를 한 번 들어보자.

내가 방 온도를 25도로 유지를하려고 한다. 현재 방 온도는 18도이고 내가 보일러에 입력하는 값은 그렇다면 25도가 될 것이다. 여기서 출력은 온도의 상승이며, 시간이 지날수록 온도는 점점 더 올라가 마지막에 25도가 될 것이다.

Sequential logic에 해당 값들을 대입해보자.

input은 25도이다.

state는 처음에는 18도였지만 갈수록 점점 높아진다.

output은 온도의 상승이다.

Sequential logic은 combination logic + Memory로 구성되어있다.

state에 해당하는 것은 memory에 저장되며, 일정 시간마다 업데이트가 되게되며 인풋값과 계속해서 반복하면서 비교를 하며 다시 state를 업데이트하게된다.

처음에는 25도와 18도를 비교해서 온도를 상승하는 출력이 나오지만 시간이 지날수록 25도와 18~25사이의 값과 비교를 하게 될 것이다.

여기서 필요한것은 얼마나 자주 업데이트를 할 것인가에 대한 이야기이다. 18도 -> 19도 -> .... 이 값을 업데이트 하는 주기가 중요한것인데 여기서 등장하는 개념이 바로 CLK이다.

이 clk에 대한 이야기를 하기전에 저장하는 memory에 대해 말하는게 먼저일거같아서 이따가 다시 이야기를 하겠다.

State를 어떻게 저장할 것인가? 정답은 바로 그 유명한 Flip-Flop을 이용하는 것이다.

Flip-Flop 1개당 1bit를 저장할 수 있는데, 위에서 state로 정수의 숫자를 0도 ~ 50도 총 51가지의 숫자를 나타내야 한다면, 6bit가 필요하다. 이 때 6개의 flip-flop을 사용해야 하는것이고,

F/F의 주요한 특징으로 Write/ Hold/ Read 이 3가지 동작을 내가 원할때(clk edge에서) 할 수 있어야한다.

3가지 동작을 clk을 고려하여 할 수 있게 만든 저장장치가 flip flop인데 이거를 한번에 보면 어려울 수 있으니, 먼저 3가지 동작이 가능하게 설계를 해보자.

먼저 Hold를 생각해보자. 값을 측정하려면 어디선가 출력이 되야한다. 즉, wire의 값을 봐야 하는데 당연하게도 gate가 이 wire의 앞에 있어야한다. 거기에 값을 "유지" 시키려면 어떻게 해야할까?

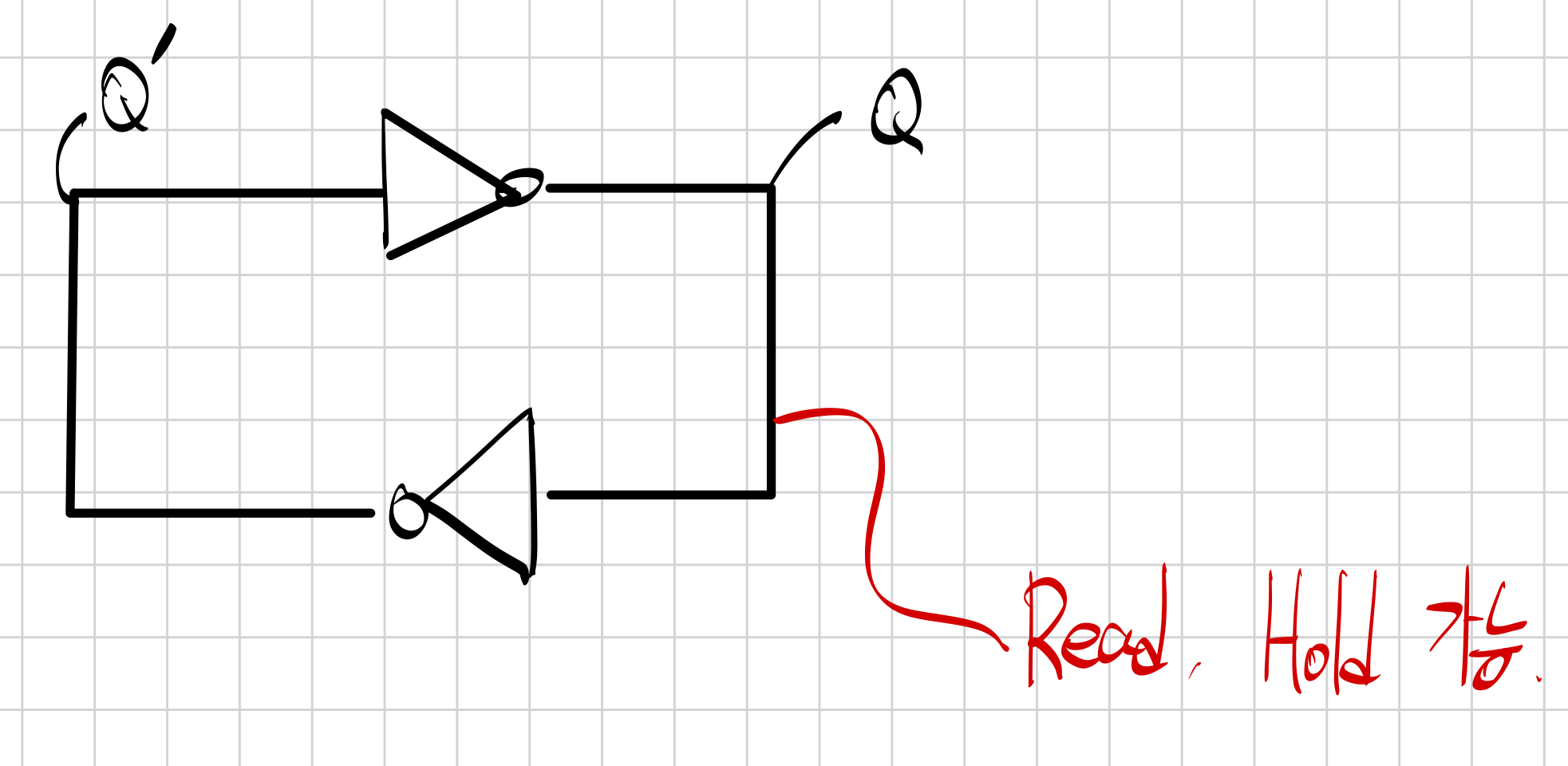

정답은 inverter 2개를 연결하고 feedback이 되게 마지막 출력을 첫번째 input으로 넣어주면 된다.

그림으로 보면 다음과 같다.

그런데 이 회로는 3가지동작중 write를 할 수 없다는 단점이 있다.

어떻게하면 write까지 가능한 회로를 만들 수 있을까?

NAND2와 NOR2을 생각해보자.

이 두가지는 단순하게 Truth-Table만을 생각하는게 아니라 다른 관점으로 암기해주는것을 강력 권장한다.

NAND의 경우 한가지 input이 1이 들어갈때 다른 input에 대한 inverter로 작동하는 gate이고,

NOR의 경우 한가지 input이 0이 들어갈때 다른 input에 대한 inverter로 작동하는 gate이다.

또한, NAND의 한가지 input이 0이 들어가면 무조건 1이 출력이되며,

NOR의 한가지 input이 1이 들어가면 무조건 0이 출력이 된다.

위 4가지는 그냥 바로 즉각적으로 사용할 수 있게 따로 외워주자. 왜 그런지는 예시를 들며 설명하겠다.

위에 inverter 2개를 붙인 그림에서 inverter를 NAND2 2개 또는 NOR2 2개로 바꿔서 다시 그려보겠다.

자세한 설명을 해보면,

첫번째 AB = 01 : NAND의 경우 0이 들어가면 무조건 1이 출력되므로 Q=1 Q' = Q의 inverse이므로 0

AB =11 : Q는 Q'의 inverter값 그러므로 Q = 1, 같은방식으로 Q = 0

AB = 10 : B=0이므로 Q' = 1, Q = Q'의 inverter값이므로 0

AB = 11 : Q는 Q'의 invertert값 그러므로 Q = 0, 같은방식으로 Q' = 1

AB = 10 또는 01일때 0일때 강제 1출력 -> 하나의 출력에 대한 inverter

AB = 11 -> 값 Hold

NOR은 같은 방식으로 진행되므로 각자 해보길 바란다.

위와 같은 방법을 Latch라고한다.

SR latch를 예시로 들면, AB가 아닌 S, R을 사용하게 되는데 set, reset이라는 의미이다.

SR latch를 NOR를 사용하게되면 S = 1일때 Q = 1, R = 1일때 Q' =1이된다. SR = 00일때 이전 값을 hold할 수 있고, SR = 11은 사용하지 않는다.

SR latch를 NAND를 사용하게 되면 S = R = 1일때 이전값을 hold, S=1, R=0일때 Q=0, Q' = 1 / S= 0, R=1일때 Q=1, Q'=0이된다. SR = 00은 사용하지 않는다. (SR에대한 출력이 둘 다 1일 수는 없으므로)

이 때, NAND기준 SR=00을 처음부터 배제를 해서 상황자체를 만들지 않을 수 있다면, 더 좋은 회로가 될 수 있지 않겠는가? Enable 신호만 옆에다 달아주면 이를 구현할 수 있다. 아래 그림을 보자.

SR=00인 상황을 애초에 제거한 것이며,

여기서 S = R일때의 상황을 없애면 En = S = R =1일때 정의가 안되는 상황을 또 줄일 수 있게 된다.

어떻게 하면 될까?

바로 밑에처럼 연결해주면된다.

위 그림이 바로 D-Latch이며, En=1일때 Q = D인 회로이다.

D-Flipflop의 경우 En=1일때가 아니라 clkedge에서만 Q=D인 회로이며,

오늘 포스팅한 회로 내부 자체를 아는것도 중요하지만 이 회로들을 하나의 모듈로 보았을때 인풋과 출력관계가 어떻게 되는지 또한 매우 중요하다.

정리를 해보면,

1. hold와 read만 되는 inverter 2개를 붙인 회로를 처음에 설계했다.

2. write도 되게 하는 회로를 만들고 싶어 inverter를 NAND2 또는 NOR2 로 바꾸었다.

3. 안되는 상황자체를 없애고 싶어서 En신호를 활용하여 회로를 약간 수정했다.

4. 어떻게 이 회로들을 설계했는지 내부 회로도 중요하지만, 하나의 큰 모듈로 봤을 때 어떻게 작동하는지도 매우매우 중요하다!

'공부 > 논리회로' 카테고리의 다른 글

| Logic_circuit_7: Register (1) | 2025.01.28 |

|---|---|

| Logic circuit_7 : Sequential Logic(2) (0) | 2025.01.16 |

| Logic_Circuit_5-Combination Logic(2)-Multiplier (0) | 2025.01.14 |

| Logic circuit_4: Combination Logic(1) (0) | 2025.01.06 |

| Logic Circuit3: Gate_Optimization (0) | 2025.01.04 |